GET TO MARKET FASTER

In the semiconductor industry, a single bug in the chip can lead to costly delays, product recalls, or even safety issues. Investment in shift-left techniques have helped to mitigate these risks by uncovering problems earlier in the semiconductor design process.

Behavioral models and High-Level Synthesis (HLS) have also enabled faster design cycles; but understanding and debugging these complex models can become a bottleneck.

By integrating time travel debugging capabilities into your design and verification flow, engineers get unprecedented visibility and access to the execution of HLS models—leading to faster time-to-market, improved design quality and increased productivity.

DEBUG ISSUES QUICKLY AND GET TO MARKET FASTER

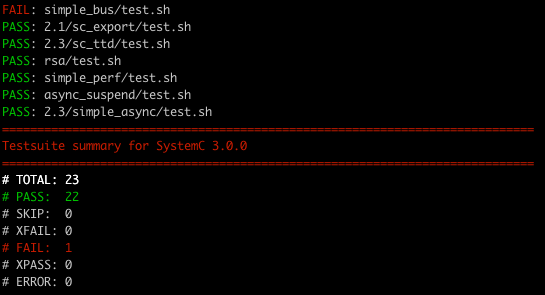

Undo allows engineers to record the execution of their failing test and later step through the recording of their simulations not just forward, but backward, making tracking bugs easier.

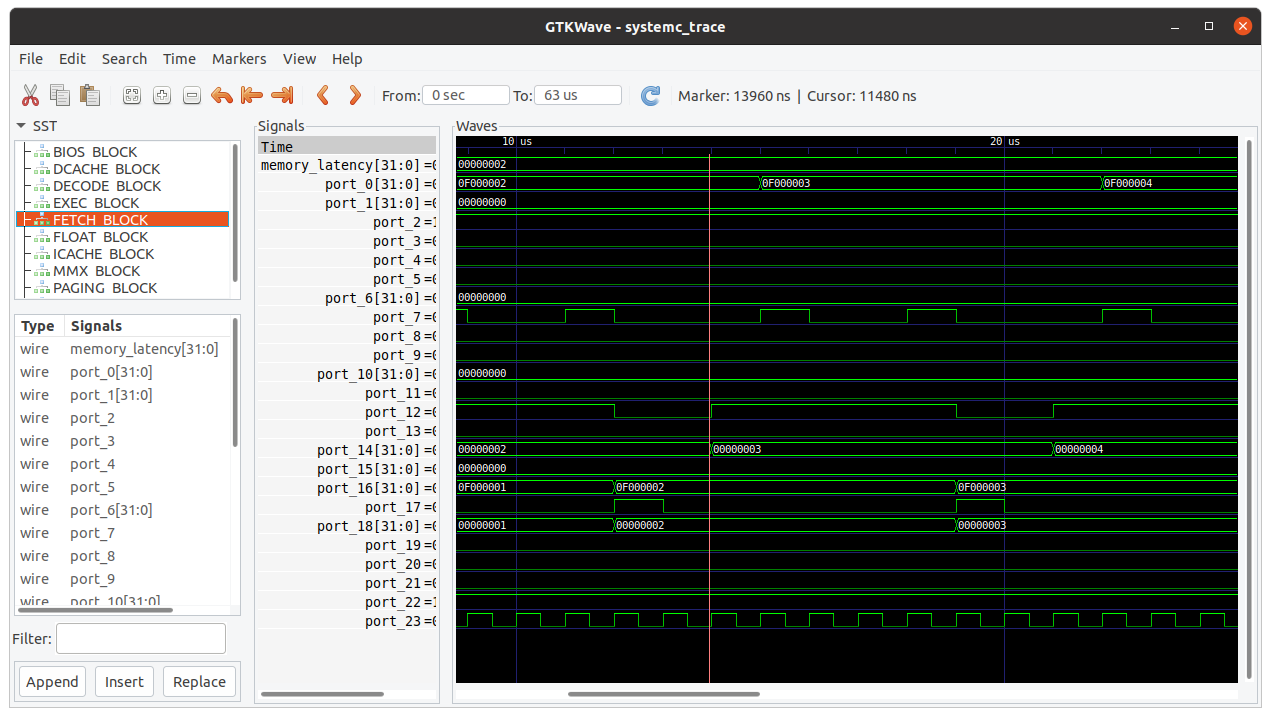

Undo also provides several features that make it easier to visualize and understand SystemC designs, like one of our beta waveform viewers.

This workflow significantly reduces the time the team spends debugging.

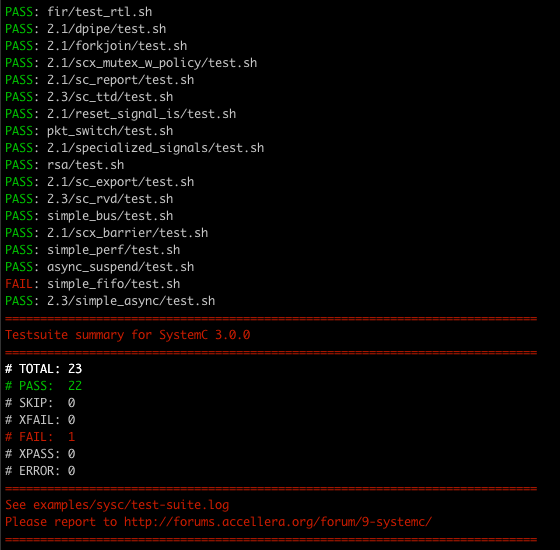

Concurrency bugs, such as deadlocks and race conditions, can take weeks to find using traditional techniques such as logging and forward-only debugging.

These kinds of bugs are pretty common in SystemC designs, where many threads can be accessing the same data and resources.

With time travel debugging we can isolate these issues very quickly.